Съдържание

- Определение - Какво означава Поетапна пинова решетка (SPGA)?

- Въведение в Microsoft Azure и Microsoft Cloud | В това ръководство ще научите за какво се занимава компютърните изчисления и как Microsoft Azure може да ви помогне да мигрирате и стартирате бизнеса си от облака.

- Техопедия обяснява поетапна решетка с пин решетка (SPGA)

Определение - Какво означава Поетапна пинова решетка (SPGA)?

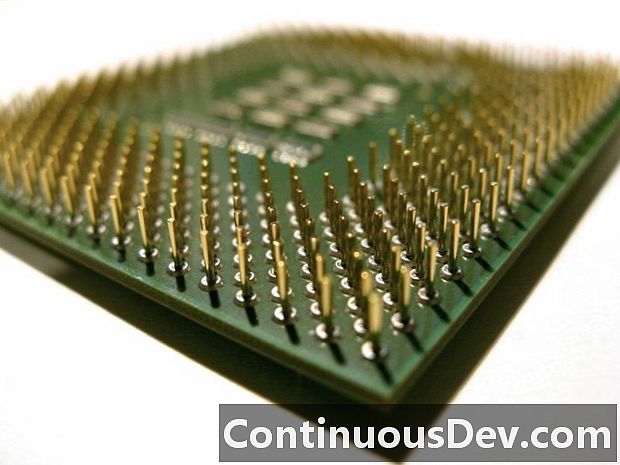

Поетапна решетка на щифтови решетки (SPGA) е стил на гнездо или интегрираща интегрална верига, имащ подредена мрежа от щифтове, заобикалящи ръба на гнездата, разположени като няколко квадрата, един в друг. Структурата е известна още като пресичащи се квадратчета.SPGA обикновено се използва на дънни платки за процесори, базирани на платформи Socket 5, Socket 7 и Socket 8.

Въведение в Microsoft Azure и Microsoft Cloud | В това ръководство ще научите за какво се занимава компютърните изчисления и как Microsoft Azure може да ви помогне да мигрирате и стартирате бизнеса си от облака.

Техопедия обяснява поетапна решетка с пин решетка (SPGA)

В подредената решетка с щифтова решетка (SPGA) щифтовете са подредени в диагонални редове. SPGA включва два квадратни масива с пинове, балансирани в двете посоки. С други думи, щифтовете са подредени така, че да образуват диагонална квадратна решетка вътре в квадратната граница. SPGA включва зона в центъра на пакета, в която не са подредени щифтове. SPGA пакетите са идеални за тези устройства, които изискват по-голяма плътност на пините в сравнение с това, което може да предложи стандартен масив с пин решетка (PGA).Първоначалните интегрални схеми имаха щифтове, подредени с помощта на PGA, която поставя щифтове в структура, подобна на решетка. Напредъкът в дизайна на процесора и търсенето на повече пинове направи PGA неподходяща и остаряла. Основната цел на SPGA беше да намали размера на микропроцесора, когато са необходими повече пинове. Структурата на SPGA се използва от процесори, съсредоточени върху технологията Socket 5, Socket 7 и Socket 8.

Предимството на използването на SPGA формация за разлика от по-ранните версии е, че се състои от по-близки щифтове, като по този начин позволява повече щифтове за конкретна повърхностна площ. Това позволява намаляване на размера на микрочипа или, с други думи, предлага по-добър капацитет за пренос в чип с подобен размер.